數位IC設計工程師[編輯] / [新增其他職務]

| 職業心智圖 | |

|---|---|

| 數位IC設計工程師 | |

| |

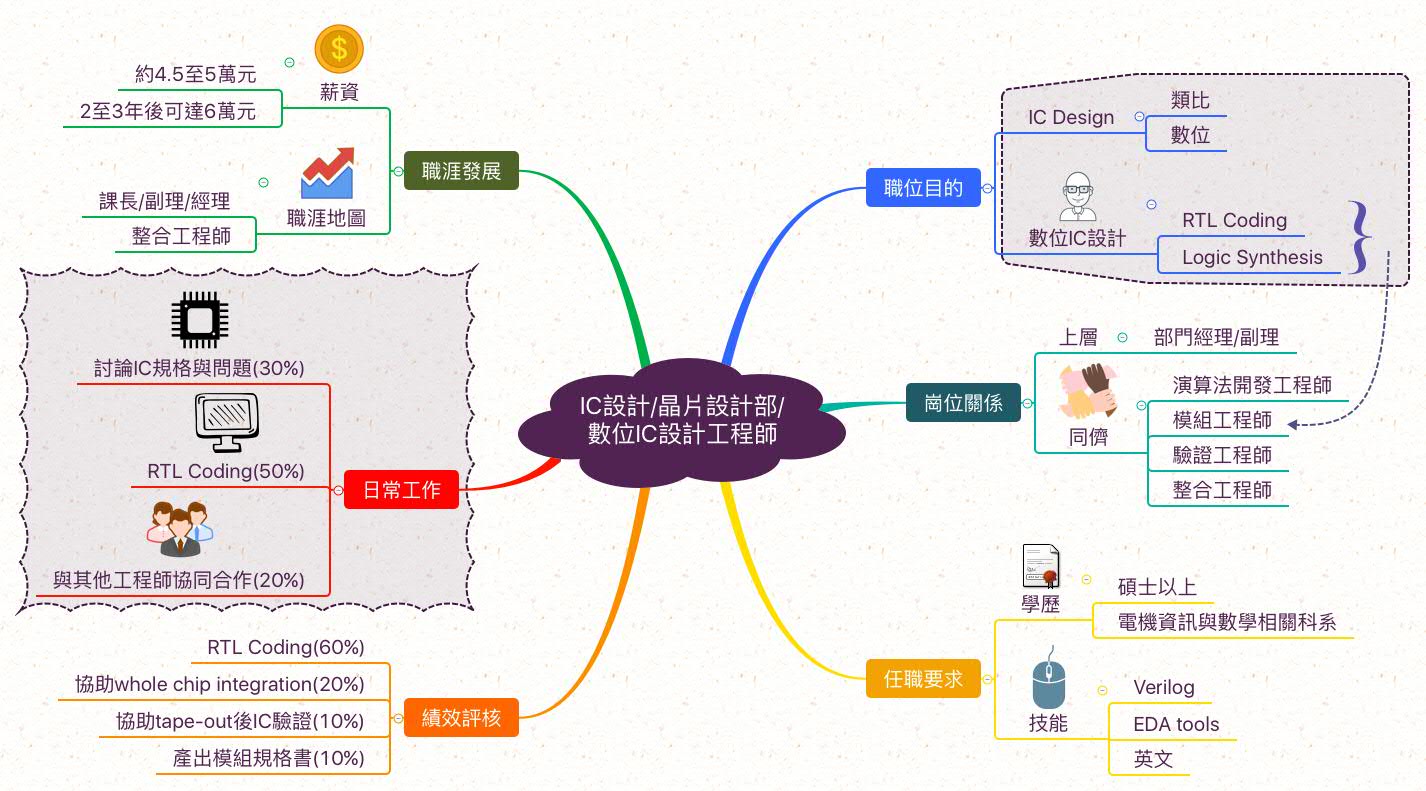

數位IC設計工程師 (半導體|IC設計|晶片設計部) IC 設計工作主要分為兩大領域,分別是數位 IC 設計與類比 IC 設計 。不過,近年來由於製程演進,加上電路愈趨複雜及整合度越來越高,邏輯閘數(Gate Count)動則超過 100M,導致數位 IC 設計工作更被細分成演算法開發、數位 IC設計、驗證工程、晶片整合設計、DFT 設計等等部分,但具體的工作分割仍要視公司的規模及開發的晶片複雜度而有定。一般而言,數位IC的開發設計遵循如下流程:

- 規格書制定

- 演算法開發

- 各個階層模組的 RTL (Register Transfer Level) Coding(邏輯電路實現)

- 電路驗證(Verification)

- 晶片整合(Chip Integration)

- 邏輯合成(Logic Synthesis)

- DFT

- Formal Verification

- 實體或佈局設計 (Physical Implementation)

- STA & Formal Verification

- 實體驗證(Physical Verification)

- Tape-out

其中, RTL Coding的工作主要是由數位 IC 設計工程師負責執行,也就是將演算法開發工程師的開發結果及目標規格書(Target Spec.)所訂定的規格做邏輯電路實現與驗證。依據年資或 公司規模與分工不同,有時工作範圍會涵蓋到邏輯合成。

職場

| 職涯探索影片 | |

|---|---|

| 廣告公司3Q時間 | |

廣告人的起手式 ?廣告的勝出關鍵?日商博報堂廣告執行創意總監陳東亨先生,精彩的職涯分享! | |

|

年度工作目標 | |

|---|---|

| 藍色 模組邏輯電路實現-RTL Coding(60%) 紅色 協助 Whole Chip Integration(20%) 橘色 協助 Tape-out 後 IC 驗證(10%) 綠色 產出模組規格書(10%) | |

|

日常工時分佈 | |

|---|---|

| 藍色 模組邏輯電路實現-RTL Coding(50%) 紅色 與主管討論規格及電路實現問題(30%) 橘色 與其他單位或工程師協同合作(20%) | |

績效評核

模組邏輯電路實現-RTL Coding(60%) : 依據規格作 RTL Coding,在符合時程規畫內開發出效能符合或 大於規格需求且 Gate Count 數在預定的範圍內 的 RTL Code。衡量標準為開發時程、電路效能、Gate Count(邏輯閘)數。

協助 Whole Chip Integration(20%) : 晶片整合工程師進行 Whole chip Integration 時,要對模組介面連線提供 必要的協助。還有在 Whole chip simulation 及 Whole chip Synthesis 方面也需提供必要的協助。衡量標準為減少整合問題、出錯率。

協助 Tape-out 後的 IC 驗證(10%) : IC 封裝回來後若 Firmware工程師對該模組的控制程序有問題或系統驗證工程師對該模組相關功能有疑問時,亦須提供協助。衡量標準為縮短系統驗證時間。

產出模組規格書(10%) : 一般在 IC Tape-out 後,各個模組都需產出各自的模組規格書或是模組報告,內容大致涵蓋演算法原理、Block Diagram、Pin Description、 模組控制程序等等。衡量標準為報告的完整度及是否依時程完成。

工作內容

與主管討論規格及電路實現遇到的問題(30%) : 常會遇到 的問題包括對目標規格的解讀不同或者是有不清楚的 地方都需要跟主管或資深的同事討論,包括如何在電路實現時可做到減少 Area 的浪費或是降低功率的消耗等等,希望能從其獲得寶 貴經驗的協助。一般來說,每週都應會有一次的部門會議 及一次與主管 one-to-one 的會議,即可透過這些會 議做適時的交流與研討。

模組的邏輯電路實現-RTL Coding(50%) : 利用TextEditor 進行 Coding,並利用 Linter (Ex: Spyglass) 進行 Coding Quality Check,然後用 Simulator(Ex:VCS) 及 Debugger (Ex: Verdi) 進行基本 Functional 的驗證並利用 Logic Synthesizer 來評估 Gate Count 及合成是否有問題等等。

與其他平行單位或工程師協同合作(20%) : 與其他模組工 程師溝通彼此的介面,與驗證工程師溝通模組驗證的需求與規格,在整合階段須協助整合工程師關於連線的問題並提供模組 clock speed 、Area、IO 等相關訊息。

崗位關係

上層:數位IC設計工程師的直屬主管為晶片設計部經/副理,大多是由資深 的數位 IC 設計工程師升任。經/副理負責管理、考核、分配工作給工程師,並在過程中給予工程師必要的指導及協助。

平行:由於每個數位IC設計工程師只會負責部分模組的設計,所以會有其他 數位 IC 設計工程師,甚至是類比 IC 設計工程師,也在同時進行其他模組的設 計,此時須跟其他IC設計工程師進行溝通或討論關於彼此模組間的輸出輸入訊號,因為若一切都等到整合時再 討論極可能會影響到 Tape-out 時程。若在分工較細的公司,平行方面還 會有驗證工程師,必須與其先溝通了解模組驗證的需求與規格,以期盡可能 將所有 Bug 都驗證出來,以減降低IC 出錯的機率。

下屬:新進的數位 IC 設計工程師不會有部屬,但在工作 2~3 年後,可能會被指派去當新進工程師的 Mentor,協助主管指導新進的工程師。

客戶 : 數位 IC 設計工程師不用接觸外部客戶,若就內部而言,則可視整合工程師為其內部客戶。

任職要求

教育程度/經驗

- 教育程度:研究所以上電子/電機/資工相關科系畢業。數位IC設計工程師比較需要邏輯觀念強的人才,因此也會有數學或機械系所畢業的人加入此一 領域。

- 經驗:數位IC設計工程師不像類比IC設計工程師較需要經驗,因此較能接受剛畢業的新人。一般來說,數位 IC 設計工程師的養成大約需要 2 年時間。

特別知識和技能

- 工程語言 : 基本 – Verilog 硬體描述語言(HDL) 、 C++ 、 TCL, 進階 -- UPF、 Perl, awk, MatLab, etc

- 工程知識 : 基本 -- 電路學、電子學、邏輯設計, 進階 -- DSP、通訊, etc

- EDA : Simulator -- VCS or IUS or Modelsim,Debugger -- Verdi, Logic synthesizer -- Design Compiler

- Formal Verification : Conformal or Formality, Linter -- Spyglass

- 語言 : 由於工作上會用到的專業文件幾乎都是用英文書寫的,再加上常有機會遇到來自國外(尤其是印度)的同事或 EDA tool Vendor,因此英文是不可或缺的基本技能。

工時薪水

薪資成長:研究所剛畢業的 IC 設計工程師起薪約在 4.5 - 5 萬元左右,經過 2-3 年的歷練後,月薪有機會上看至 6 萬元以上。

升遷機會:資深的數位IC設計工程師看表現有機會逐步升任晶片設計部課長 /副理 /經理,或是可轉換成為整合工程師。